典型的晶振電路

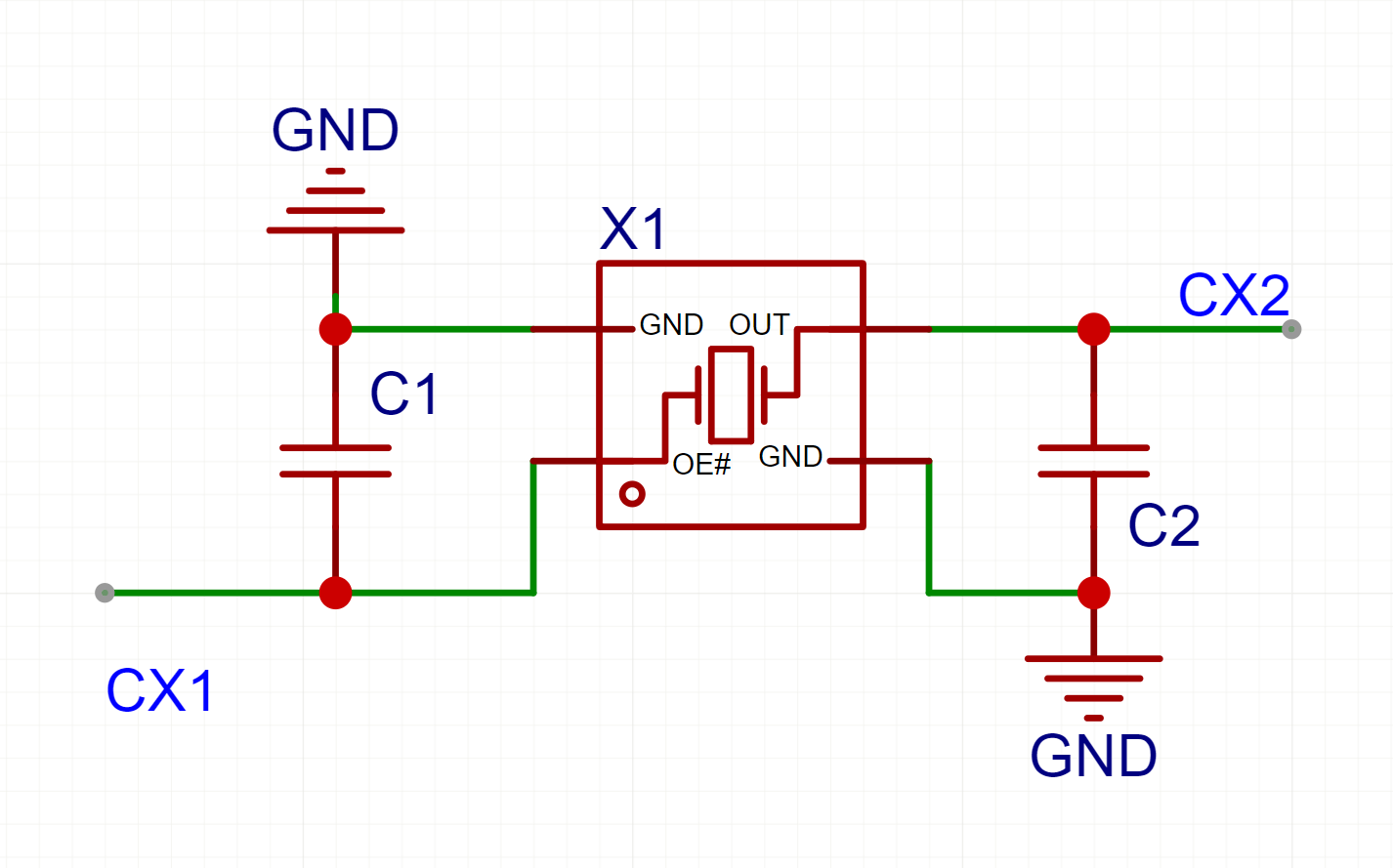

這是一個典型的晶振電路:

晶振外部有2個電容, 一般取值相同. 這2個電容有多種叫法,比如匹配電容,負載電容,外接電容等, 以下簡稱匹配電容(${C_1}$,${C_2}$) .

晶振本身有一個指標負載電容${C_L}$(Load capacitance),負載電容是指晶振要正常震盪所需要的電容,是指晶振的兩條引線連接IC塊內部及外部所有有效電容之和,可看作晶振片在電路中串接電容。一般購買晶振時會標註這個參數.

匹配電容是負載電容的一部分.

一般情況下,增大負載電容會使振盪頻率下降,而減小負載電容會使振盪頻率升高。

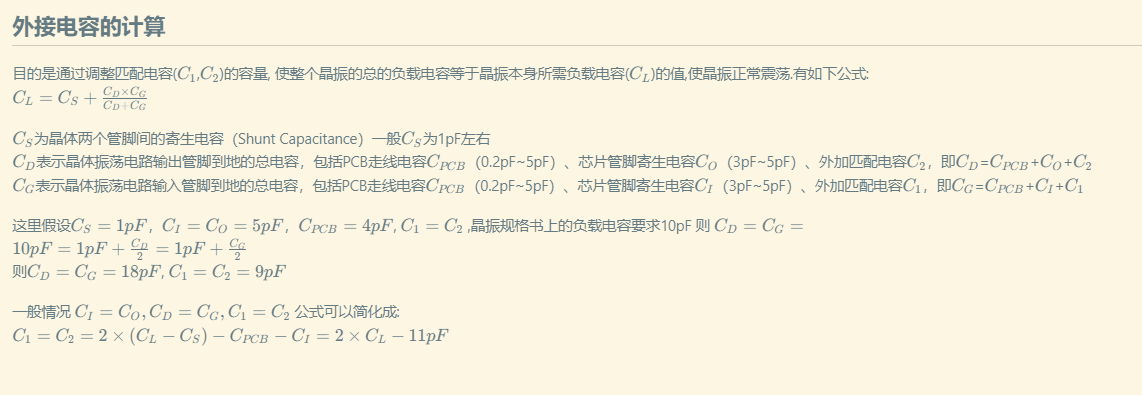

外接電容的計算

目的是通過調整匹配電容(${C_1}$,${C_2}$)的容量, 使整個晶振的總的負載電容等於晶振本身所需負載電容(${C_L}$)的值,使晶振正常震盪.有如下公式:

${C_L}={C_S}+\frac{C_D \times C_G}{C_D + C_G}$

${C_S}$為晶體兩個管腳間的寄生電容(Shunt Capacitance)一般${C_S}$為1pF左右

${C_D}$表示晶體振盪電路輸出管腳到地的總電容,包括PCB走線電容${C_{PCB}}$(0.2pF~5pF)、芯片管腳寄生電容${C_O}$(3pF 5pF)、外加匹配電容${C_2}$,即${C_D}$=${C_{PCB}}$+${C_O}$+${C_2}$5pF)、芯片管腳寄生電容${C_I}$(3pF ~5pF)、外加匹配電容${C_1}$,即${C_G}$=${C_{PCB}}$+${C_I}$+${C_1}$

${C_G}$表示晶體振盪電路輸入管腳到地的總電容,包括PCB走線電容${C_{PCB}}$(0.2pF

這裡假設${C_S}=1pF$,${C_I=C_O}=5pF$,${C_{PCB}=4pF}$, ${C_1=C_2}$ ,晶振規格書上的負載電容要求10pF 則$ {C_D=C_G=}$

${10pF=1pF+\frac{C_D}{2}=1pF+\frac{C_G}{2}}$

則${C_D=C_G=18pF}$, ${C_1=C_2=9pF}$

一般情況 ${C_I=C_O},{C_D=C_G},{C_1=C_2}$ 公式可以簡化成:

${C_1=C_2={2}\times{(C_L-C_S)}-C_{PCB}-C_I={2}\times{C_L-11pF}}$